Tugas 6 oakti Pertemuan 6

Nama: Ihsannur Fathan Riziq

Kelas : TI 2A

NIM : 2103015135

BUS SISTEM

Program

Suatu

deretan langkah-langkah dikerjakan suatu operasi arithmetic atau logical.

Fungsi Control Unit

Untuk setiap operasi disediakan kode yang unik

Contoh: ADD, MOVE Bagian hardware tertentu

menerima kode tersebut kemudian

menghasilkan sinyal-sinyal kendali.

Komponen yang diperlukan: Control

Unit (CU) dan Arithmetic and Logic Unit

(ALU) membentuk Central Processing Unit (CPU)

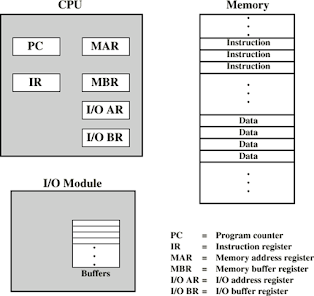

Komponen Komputer Top level view:

Siklus Instruksi:

Memiliki 2 Steps yaitu Fetch Cycle dan Execute Cycle

Fetch Cycle:

1. Program Counter (PC) berisi address instruksi berikutnya yang akan diambil

2. Processor mengambil instruksi dari memory pada lokasi yang ditunjuk oleh PC

Execute Cycle:

1. Processor-memory : Transfer data antara CPU dengan main memory

2. Processor I/O : Transfer data antara CPU dengan I/O module

3. Control : 1. Mengubah urutan operasi

2. Contoh : Jump

Contoh Ekseskusi Program

Suatu mekanisme yang disediakan bagi modul-modul lain (mis. I/O) untuk dapat meng-interupsi operasi normal CPU

Contoh : Overflow, division by zero

Siklus Interrupt

1. Ditambahkan ke instruction cycle

2. Processor memeriksa adanya interrupt (Diberitahukan lewat interrupt signal)

3. Jika tidak ada interrupt, fetch next instruction

4. Jika ada interrupt:

1. Tunda eksekusi dari program saat itu

2. Simpan context

3. Set PC ke awal address dari routine interrupt handler

4. Proses Interrupt

5. Kembalikan context dan lanjutkan program yang terhenti

DIAGRAM DENGAN SIKLUS INSTRUKSI DENGAN INTERRUPT

1. Disable interrupts : 1. Processor akan mengabaikan interrupt berikutnya

2. Interrupts tetap akan diperiksa setelah interrupt ynag pertama selesai dilayani

3. Interrupts ditangani dalam urutan sesuai datangnya

2. Define Priorities : 1. Low priority interrupts dapat di interrupt oleh higher priority interrupts

2. Setelah higher priority interrupt selesai dilayani, akan kembali ke interrupt sebelumnya.

BUS

Jalur komunikasi yang menghubungkan beberapa device,Biasanya menggunakan cara broadcast.

Dikelompokan menjadi 2 bagian antara lain:

1. Satu bus berisi sejumlah kanal (jalur)

2. Contoh bus data 32-bit berisi 32 jalur

Data bus

1. Membawa data

2. Lebar jalur menentukan performance (8,16,32,64 bit)

Adress bus

1. Menentukan asal tujuan dari kata

2. Misalkan CPU perlu membaca instruksi (data) dari memori pada lokasi tertentu

3. Lebar jalur menentukan kapasitas memori maksimum dari sistem

contoh : 8080 memiliki 16 bit address bus maka ruang memori maksimum adalah 64k

Control Bus

Informasi kendali dan timing

1. Sinyal read/write memory (MRD/MWR)

2. Interrupt request (IRQ)

3. Clock Signals (CK)

SKEMA INTERKONEKSI BUS

JENIS BUS

1. Dedicated

2. Multiplexed

Arbitrasi bus

1. Beberapa modul mengendalikan bus

2. contoh CPU dan DMA controller

3. Setiap saat hanya satu modul yg mengendalikan

4. Arbitrasi bisa secara centralised atau distributed

Arbitrasi Centralised

1. satu hardware yang mengendalikan akses bus

a. Bus controller

b. Arbiter

2. Bisa berupa bagian dari CPU

Arbitrasi Distributed

1. Srtiap module dapat mengklaim bus

2. Setiap modules memiliki Control Logic

BUS PCI

1. Arbitrasi bisa secara centralised atau distributed

2. Dikeluarkan oleh Intel sebagai public domain

3. 32 atau 64 bit

4. 50 Jalur

JALUR PADA BUS PCI (WAJIB)

1. Jalur System

2. Address & data

3. Interface Control

4. Arbitrasi

5. Error lines

JALUR PADA BUS PCI (OPTIONAL)

1. Interrupt lines

2. Cache support

3. 64-bit Bus Extension

4. JTAG/Boundary Scan

COMMAND pada PCI

1. Transaksi antara initiator (master) dg target

2. Master pegang kendali bus

3. Master menentukan jenis transaksi

4. Fase Address

5. Fase data

SOAL

1. proses penghubungan berbagai komponen logik pada konfigurasi yang diinginkan untuk membentuk operasi aritmatik dan logik pada data tertentu merupakan pengertian dari....

a. Cache support

b. Data system

c.Pemograman

d. Error lines

2. Siklus intruksi memiliki 2 cara yaitu.......

a. Fetch Cycle dan execute Cycle

b. Dedicated dan Multiplexed

c. CPU dan DMA

d. Fase address dan fase data

3. Program Counter (PC) berisi address instruksi berikutnya yang akan diambil merupakan pengertian dari......

a. Error lines

c. Cache

d. CPU

4. Suatu mekanisme yang disediakan bagi modul-modul lain (mis. I/O) untuk dapat meng-interupsi operasi normal CPU dinamakan.....

a. Error lines

b. Interrupt

c. Arbitrasi

d. Domain

5. Multiple Interrupts memiliki 2 macam, Salah satunya adalah.....

a. Fetch Cycle

b. Domain System

c. Disable interrupts

d. Memory

6. Jalur komunikasi yang menghubungkan beberapa device merupakan pengertian dari.....

a. BUS

b. CPU

c. Cache

d. DMA

7. Jalur data & address terpisah merupakan ciri-ciri dari Jenis Bus........

a. Dedicated

b.Multiplexed

c.Arbitrasi

d. Domain

8. BUS PCI memiliki ....... jalur

a. 70

b. 90

c. 50

d. 89

9. Macam-macam jalur pada bus PCI yang wajib kecuali....

a. Error lines

b.Jalur System

c. Arbitrasi

d. Domain

10. Macam-macam jalur pada bus PCI yang optional kecuali....

a. Cache Support

b. JTAG

c. Interrupt lines

d. Error lines

Komentar

Posting Komentar